Xilinx Vivado 도구를 위한 10G 이더넷 교환기 IP 커널

10G 망관 이더넷 스위치 IP는 Xilinx Vivado IPI 툴에 통합되어 있다. 이 그래픽 인터페이스는 높은 수준의 시점으로부터 IP의 일반적인 매개변수를 구성할 수 있도록 한다. 합성 시간에 이러한 유연성이 있기 때문에 주어진 응용 프로그램 및 장치의 기능과 포트 측면에서 최적화된 구현을 얻는 것이 가능하다. 또한 모든 HDL 언어를 사용하여 IP를 직접 인스턴스화할 수 있다.

10G 관리 이더넷 교환기 IP 코어

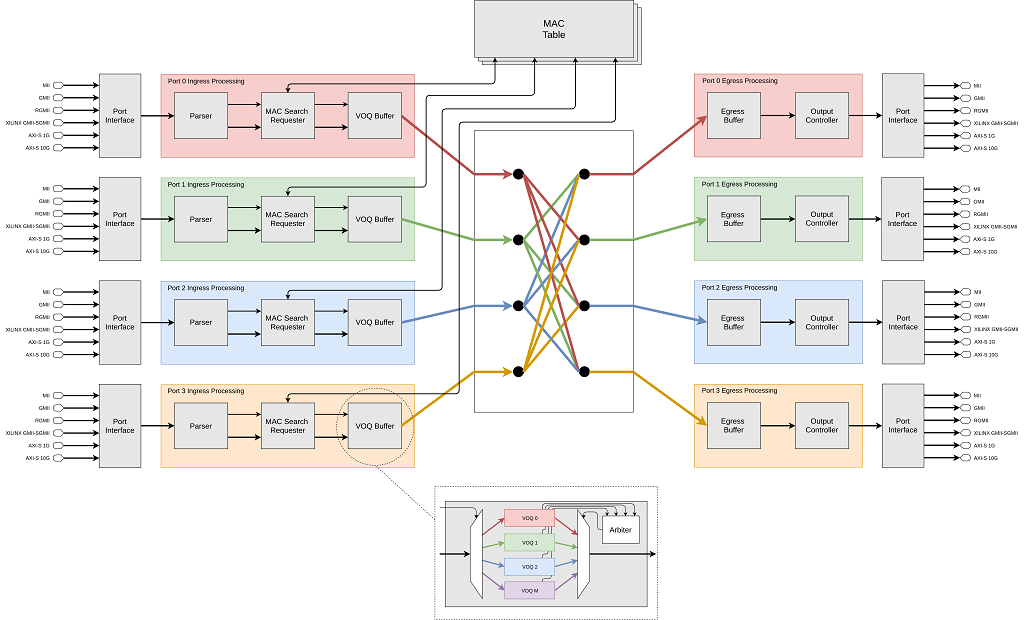

10G 관리 이더넷 교환기(MES) IP커널은 전속 팀 헤드 효과 임의 교차 매트릭스가 있으며 모든 포트 간의 연속 전송을 허용한다. 32개에 달하는 포트를 지지하고 다양한 선속이 있다. 본 교환기는 프레임 무결성 검사에 대한 이더넷 표준 정책을 만족시키는 저장및 전달 전환 방법을 구현한다.

내부 미세구조는 핵심용 사례에서 교환기의 신뢰성을 확보할 수 있다. 예를 들어 가상 출력팀열 조합의 거울상은 MAC 표토량 동시 방문 행렬을 허용했다. IP는 외부 메모리 없이 요청하지 않는다.

10G MES는 다중 속도(100M/1G/2.5G/5G/10Gs) 스위치 IP이며 IEEE 1588 V2 투명 클럭 기능을 지원한다. 이 기능은 PTP 이벤트 메시지를 수정하고 스위치를 통과하는 데 걸리는 시간을 고려한다. 본 고안은 네트워크 전체의 전송차이를 보상하여 전송정확도를 향상시킨다. 구체적으로, 10G MES는 또한 각 포트가 독립적인 하드웨어를 사용하도록 하여 IEEE 1588 V2 One Step 투명 시계 피어(P2P) 기능을 지원한다. 이 기능은 체류 시간뿐만 아니라 각 링크의 지연도 보상해 준다.

10G MES는 다중 속도(100M/1G/2.5G/5G/10Gs) 스위치 IP이며 IEEE 1588 V2 투명 클럭 기능을 지원한다. 이 기능은 PTP 이벤트 메시지를 수정하고 스위치를 통과하는 데 걸리는 시간을 고려한다. 본 고안은 네트워크 전체의 전송차이를 보상하여 전송정확도를 향상시킨다. 구체적으로, 10G MES는 또한 각 포트가 독립적인 하드웨어를 사용하도록 하여 IEEE 1588 V2 One Step 투명 시계 피어(P2P) 기능을 지원한다. 이 기능은 체류 시간뿐만 아니라 각 링크의 지연도 보상해 준다.

IP는 이더넷 PHY 장치를 위한 MII/GMII/RGMII 네이티브 인터페이스를 포함하며 Xilinx IP와 결합하여 RMII/SGMIIQ/SGMII 및 USXGMII와 같은 인터페이스를 지원할 수 있다. 또한 AXI4-Stream 인터페이스를 제공하여 SAS crypt와 같은 다른 IP 커널과의 연결을 단순화하여 선속 보안을 실현한다.

인터페이스

●전이중 100M/1G/2.5G/5G/10G 이더넷 인터페이스

●이더넷 포트 3개부터 32개까지 구성 가능

●MII/RMII/GMII/RGMII/SGMII/QSGMII/USXGMII 물리층 장비(PHY) 인터페이스

●포트마다 다른 데이터 속도 지원

●동케이블과 광섬유매체 인터페이스 :

100M/1G/2.5G/5GBase-T, 100MBase-FX, 1GBase-X, 10GBase-SR, 10GBase-LR, 10GBase-BX

교환

●자동 MAC 주소 학습과 에이징 기능이 있는 동적 MAC 표

●정적 MAC 테이블

●점보 프레임 관리

●이더넷 기반 교환

●포트 미러링

●라디오/멀티캐스트 폭풍 보호

●포트당 속도 제한(방송, 멀티캐스트, 유니캐스트 트래픽)

시간 동기화

●IEEE 1588v2 무상태 투명 시계 기능 (P2P – 레이어 2 / E2E – 레이어 2)

●호환 SoC-e IEEE 1588 IP 코어(1588Tiny,PreciseTimeBasic)

유통 관리

●멀티캐스트 프레임 필터링

●포트 마스크 교환: 사용자 정의 프레임을 특정 포트로 전달

●포트 기반 VLAN 지원

●서비스품질(QoS)

우선순위(PCP-802.1p, DSCP TOS, 이더넷 타입)

●IEEE 802.1X EAPOL 하드웨어 처리

●DSA(분산 스위치 구조) 태그:DSA를 사용하는 이상적인 시나리오는 이더넷 스위치가 “스위치 태그”를 지원하는 하드웨어 기능이다. 이 기능은 스위치가 각 이더넷 프레임에 대해 특정 태그를 삽입하고, 이 프레임이 특정 포트로부터 수신되어 관리 인터페이스의 결정을 돕는다.

프레임은 어느 포트에서 온 것입니까?

이 프레임을 전달한 이유는 무엇입니까?

CPU가 시작한 트래픽을 특정 포트에 보내는 방법

배치

●MDIO, UART, AXI4-Lite 또는 CoE(이더넷 구성) 관리 인터페이스

●이더넷 구성(COE): CPU에 연결된 동일한 이더넷 링크를 통해 내부 레지스터에 전면 액세스

● IP 커널 구매 시 드라이버 제공

중복 프로토콜

●M/RSTP (소프트웨어 스택 필요)

M/RSTP에 대한 하드웨어 지원

IP 커널과 함께 제공되는 리눅스 레퍼런스 M/RSTP 스택

Posix 호환 RSTP 스택 제공

지원되는 Xilinx FPGA 시리즈 및 평가판

우리의 TGES IP 커널은 다음 Xilinx 시리즈에 배포될 수 있다. 다음 링크에서 서로 다른 Xilinx 제품 시트와 선택 가이드를 찾을 수 있다

●7-Series (Zynq SoC, Spartan, Artix, Kintex, Virtex)

●Ultrascale (Kintex, Virtex)

●Ultrascale+ (Zynq MPSoC, Kintex, Virtex)

●Versal ACAP

디자인 지원 보드 참조:

하드웨어 플랫폼의 경우 SoC-e에서 IP 커널의 사전 로드 설계에 이러한 모듈을 제공할 수 있는 시스템 레벨 모듈(SoM)도 개발했다. 이 경우 우리의 SoM은 네트워크 애플리케이션을 위해 특별히 개발되었다. 우리는 7 시리즈, Ultrascale 또는 Ultrascale + Xilinx FPGA 시리즈를 기반으로 하는 SoM을 가지고 있다.

우리의 10G 이더넷 스위치에 대해 우리는 다음과 같은 하드웨어를 추천한다.

●SoC-e 10G MES KIT:Xilinx ZU106 보드, SFP+ 케이지 FMC, 10G 광섬유 SFP+, 광섬유 양방향 LC 테일

다운하기: 10G MES – 100M1G2.5G5G10G관리 이더넷 교환기 IP 코어