1G UES – 비관리 이더넷 스위치 IP 코어

비관리 이더넷 스위치 IP 코어(UES)는 구성 가능한 장치에서 플러그 앤 플레이 이더넷 스위치 를 구현한 다. 외부 구성이 필요하지 않으며 최소 리소스를 사용하여 최대 처리량을 해결하도록 설계되었다.

본 교환기 는 모든 포트 간의 선속 통신을 허용하는 차단되지 않은 교차 스위치 매트릭스를 구현한다. 스위치는 각 프레임을 전송하기 전에 먼저 캐시하고 검증한다. 그러나 대기 시간은 나노초 수준으로 최소화되었다. 또한 UES는 IEEE 1588 V2 투명 클럭 기능을 지원한다. 이 기능은 도입 스위치에서 생성된 잘못된 PTP 프레임을 수정하여 IEEE 1588 동기화 장치 간의 상호 연결이 가장 높은 수준의 정확도를 유지하도록 한다.

UES는 이더넷 기반 산업 네트워크를 구현하는 이상적인 이더넷 스위치 IP 다. 이더넷 PHY 장치에 MII/GMII/RGMII 네이티브 인터페이스를 제공하며 Xilinx IP와 결합하여 다른 인터페이스에서 RMII 또는 SGMII를 지원할 수 있다. 또한 MAC 기반 인터페이스가 없는 다른 IP 커널에 AXI4-Stream 인터페이스를 연결할 수 있도록 지원한다.

이하 Xilinx FPGA시리즈는 UES 지지한다.

7-Series (Zynq, Spartan, Artix, Kintex, Virtex)

Ultrascale (Kintex, Virtex)

Ultrascale+ (Zynq MPSoC, Kintex, Virtex)

Versal ACAP

Xilinx Vivado 도구용 비망관 이더넷 스위치 IP 커널

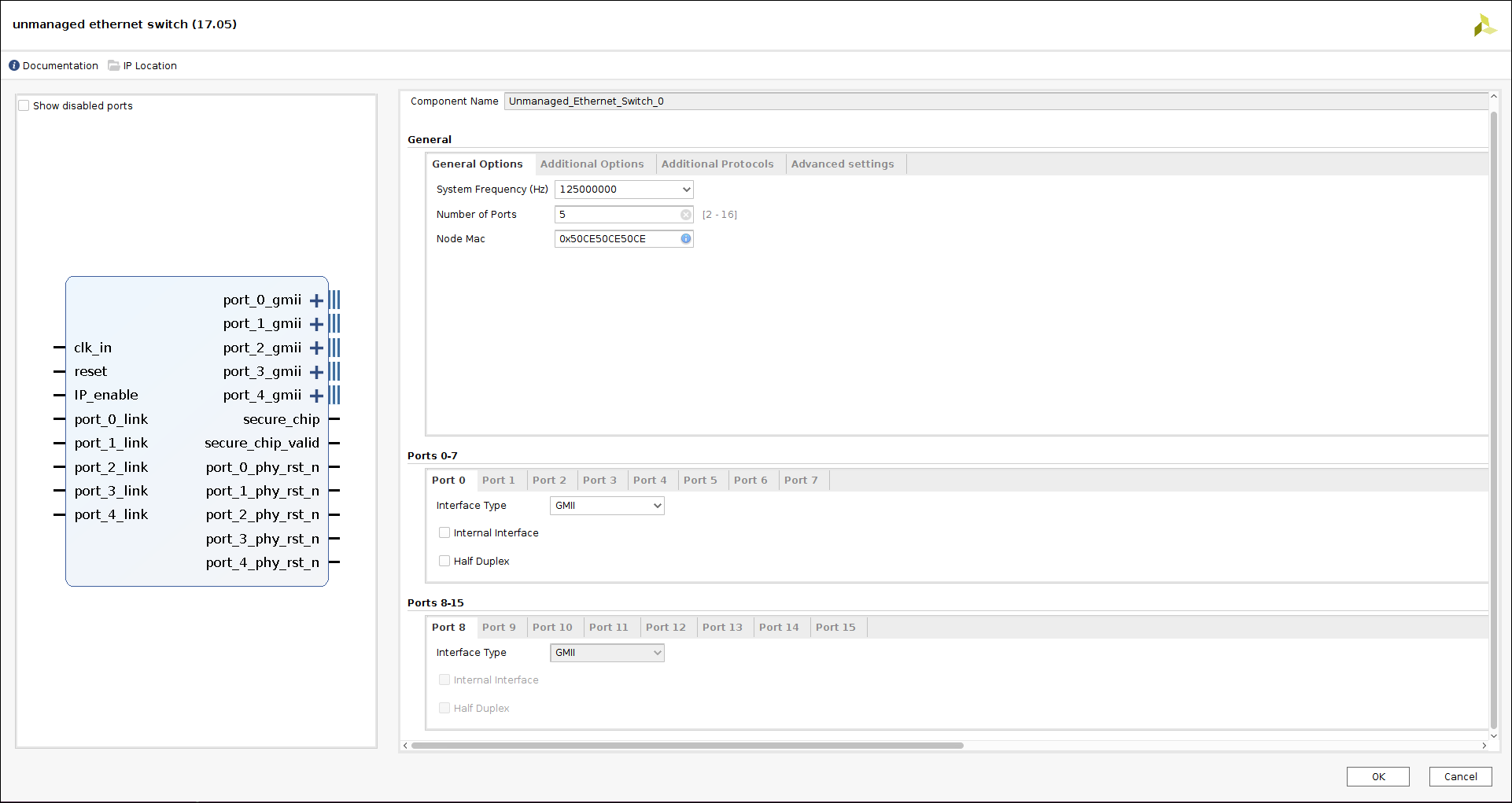

새로운 Xilinx Vivado 도구를 사용하여 그래픽 사용자 인터페이스에서 IP 커널을 사용하고 간단한 방식으로 IP 매개변수를 구성할 수 있는 FPGA 설계에 UES를 쉽게 통합할 수 있다.

비관리 이더넷 스위치 IP 코어 의 주요 기능:

●플러그 앤 플레이: 구성 불필요

●고성능: 포트 간 풀 크로스 매트릭스 구현으로 최대 처리량 달성

●빠른 시간: SoC-e만의 MAC 주소 매칭 메커니즘으로 지연시간 대폭 단축

●효율성: 최적화되어 적은 논리 자원만으로 저비용 FPGA 디바이스에서 실현 가능

●유연성: 최적의 기능-사이즈 밸런스를 위해 완전히 확장 가능하고 구성 가능합니다.다음 매개 변수 디자이너를 사용할 수 있습니다.

포트 수: 설정 가능한 이더넷 포트 3개에서 16개

버퍼 대기열 길이

IEEE 투명 시계 기능

●자동: MAC 주소 학습 및 노후화(기본적으로 저장 용량은 MAC 주소 2048개).

SoC-e SMARTzynq brick(추천)

1G UES – 비관리 이더넷 스위치 IP 코어