10G MTSN – 다포트TSN 교환기 IP 코어

애플리케이션에 최적화된 TSN 브리지나 엔드포인트 장치를 구축하세요

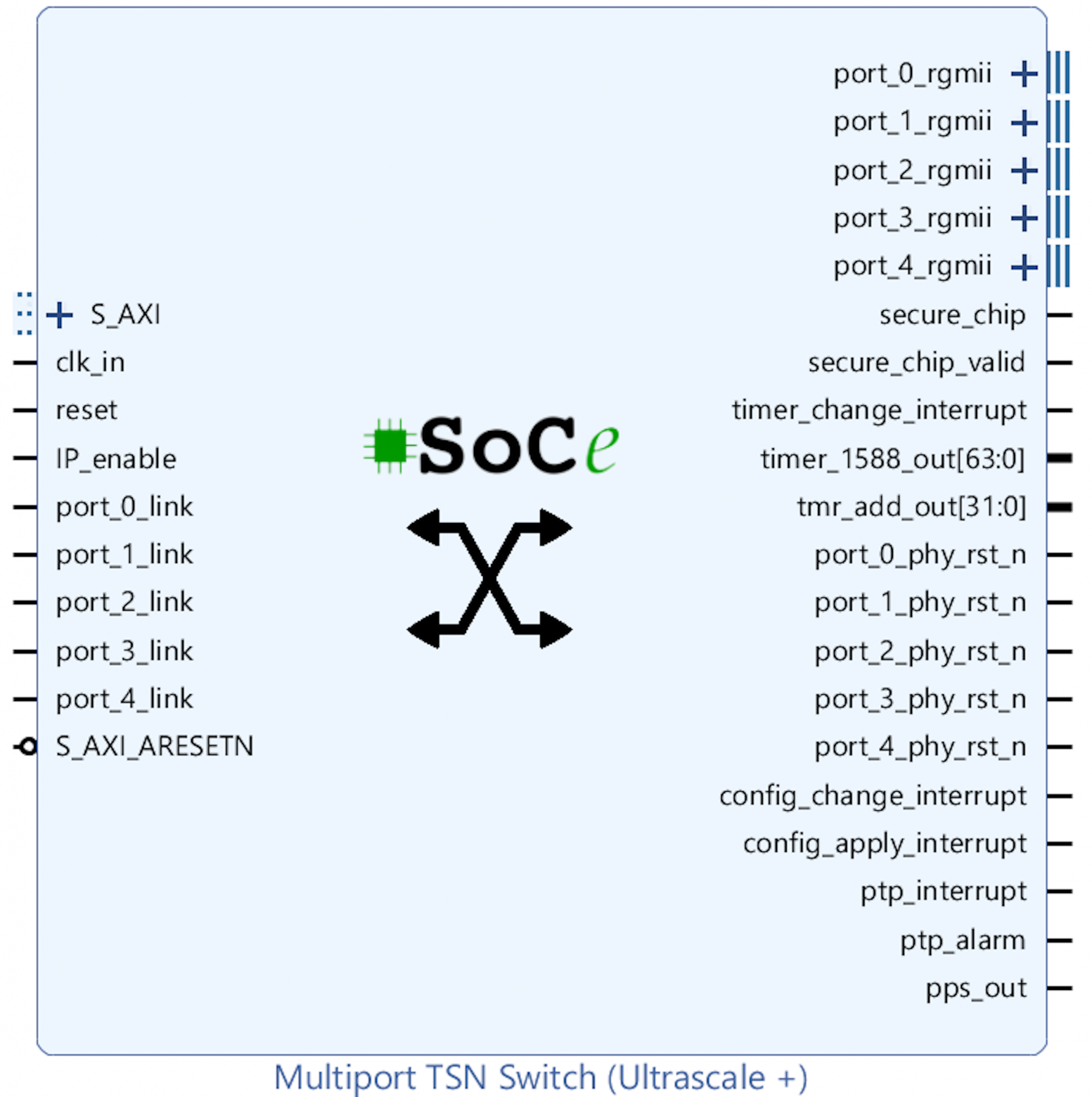

SOC-E SocTek 시리즈 10G TSN 이더넷 스위치 IP 코어는 MTSN 스위치 IP 코어의 최신 버전입니다. 또한 유연한 HDL 코드로서 TSN 엔드포인트나 TSN 브리지 구현을 생성할 수 있으나 10G 포트를 선택할 수 있습니다. 다른 SoC-e IP 코어와 마찬가지로, 이 IP는 기능 자원의 최적의 절충을 위한 풍부한 공통 매개변수를 가지고 있습니다. 이 일반 코드들은 Vivado GUI를 통해 그래픽으로도 구성할 수 있습니다.

기능

배포 지원

기능

인터페이스

- 풀 듀플렉스 100M/1G/2.5G/5G/10G 이더넷 인터페이스

- 최대 32개의 이더넷 포트를 구성할 수 있습니다

- MII/RMII/GMII/RGMII/SGMII/QSGMII/USXGMII 물리 계층 장치(PHY) 인터페이스. (다른 분들은 저희에게 연락해 주세요)

- 각 포트는 서로 다른 데이터 속도를 지원합니다

교환

- 자동 MAC 주소 학습 및 연령 관리 기능이 있는 동적 MAC 테이블

- 정적 MAC 테이블

- 점보 프레임 관리

- 방송/멀티캐스트 폭풍 보호

- 포트별 속도 제한 (방송, 멀티캐스트, 유니캐스트 트래픽)

- 포트 기반 VLAN 지원

저수준 구성

- MDIO, UART, AXI4-lite 관리 인터페이스.

- IP 코어를 구매할 때 드라이버가 제공됩니다

고급 구성

- NETCONF YANG 모델 지원 (CNC 구성)

- 고급 구성 GUI

시간에 민감한 네트워킹

- IEEE 802.1AS(rev)는 시간 동기화 계층에 사용됩니다

- IEEE 802.1Qav는 트래픽 예약에 사용됩니다

- 크레딧 기반 셰이퍼: 각 트래픽 카테고리별로 대역폭 예약을 구성할 수 있습니다

- IEEE 802.1Qbv는 트래픽 계획에 사용됩니다

- 시간 인식 셰이퍼: 구성할 수 있는 타임 슬롯의 수입니다

- IEEE 802.1Qcc 네트워크 관리

- NETCONF는 YANG 데이터를 관리하는 데 사용됩니다

- IEEE 802.1Qci 데이터 흐름 필터링 및 규제 (*)

- LLDP (링크 계층 탐색 프로토콜)용 IEEE 802.1AB

- IEEE 802.1w 고속 스패닝 트리 프로토콜

- IEEE 802.1s 다중 트리 프로토콜

- IEEE 802.1CB 프레임 복제 및 신뢰성 취소 (*)

- IEEE 802.1Qbu/802.3br 프레임 선점 (*)

*향후 버전 또는 상호운용성 테스트 대기 예정

배포 지원

지원되는 자일링스 FPGA 평가 보드

SOC-E SocTek 시리즈 10G MTSN IP 코어는 다음 Xilinx 시리즈에 배치될 수 있습니다. 다음 링크에서 다양한 자일링스 제품 시트와 선택 가이드를 찾으실 수 있습니다:

- 7 시리즈 (Zynq, Spartan, Artix, Kintex, Virtex)

- 울트라스케일(Kintex, Virtex)

- Ultrascale+(Zynq MPSoC, Kintex, Virtex)

- 버살 ACAP

평가 보드에는 SOC-E의 IP 코어를 사전 장착된 설계로 제공하는 System-on-Module(SoM)도 도입했습니다. SOC-E는 7 시리즈, 울트라스케일, 또는 울트라스케일+ 자일링스 FPGA 계열 기반의 SoM을 제공할 수 있습니다.

제품 추천

SOC-E

릴리움 시리즈

RELY-TSN-PCIe

TSN NIC 카드

SOC-E

릴리움 시리즈

RELY-TSN-BRIDGE

TSN 스위치

SOC-E

릴리움 시리즈

RELY-TSN-LAB

TSN 테스트 도구

SOC-E

릴리움 시리즈

RELY-TSN-REC

TSN 기록기