SpaceWire IP 코어

SpaceWire 프로토콜은 센서, 대용량 메모리, 처리 장치 및 하향링크 원격 측정 하위 시스템 간의 상호 연결을 단순화하는 고속 링크 및 네트워크에 대한 우주선 표준이다. 전이중, 양방향, 직렬, 피어 투 피어 데이터 링크다. 데이터를 각 방향으로 두 개의 차분 쌍을 사용하여 인코딩한다. 총 8개의 신호선이 있으며 각 방향에는 4개가 있다. SpaceWireRDDP는 우주선 시스템, 버스 시스템 및 임베디드 마이크로컨트롤러와 같은 많은 항공 우주 마이크로전자 장치에 적합할 수 있다. 유럽우주국(ESA)은 NASA, JAXA 및 RKA를 포함한 국제 우주 기관과 협력하여 우주선 통신 네트워크 표준의 진화를 조정했다.

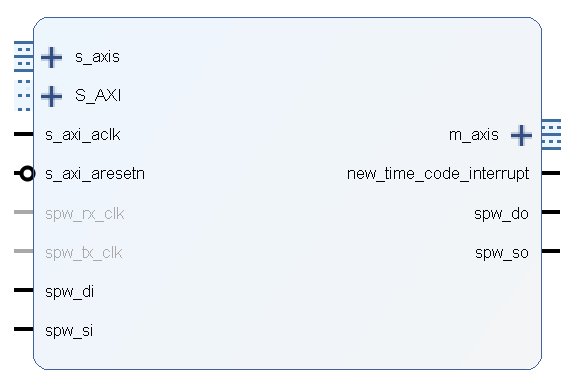

SpaceWire IP 코어는 VHDL 커널로 AXI 관리 인터페이스가 있는 완전하고 신뢰할 수 있으며 빠른 SpaceWire 코덱을 구현하여 FPGA 및 구성 가능한 SoC 장치를 합성한다.

IP 코어는 ‘대상 주소’가 없는 피어 투 피어 링크에서 패킷 수준으로 실행될 수 있다. ECSS-E-ST-50-12C에 맞게 설계되었으며 SpaceWire IP는 범용 및 빠른 구현 모드를 지원하며 송신기는 최대 5배의 시스템 클럭 주파수를 지원하도록 설계되었다.

SpaceWire IP는 그래픽 사용자 인터페이스에서 IP 커널을 사용하고 간단한 방식으로 IP 매개변수를 구성할 수 있는 새로운 Xilinx Vivado 도구를 사용하여 FPGA 설계에 원활하게 통합될 수 있다.

소개

배포 지원

다운하기

소개

SpaceWire IP 코어의 주요 기능:

데이터 인터페이스

●시스템 클럭 주파수만큼 Rx 비트 전송률이 높은 x4

●Tx 클럭 주파수는 100MHz-625MHz 사이

●단독 클럭 필드

FIFO 배치

●Tx FIFO 깊이 설정 가능: 64바이트에서 16384바이트

●RX FIFO 깊이 설정 가능: 64바이트에서 16384바이트

인터페이스

●AXI 스트림 (데이터)

●AXI-4 Lite (구성 및 관리)

성능

●최대 200Mbps의 링크 속도

SoC-e의 SMARTcia 보드는 SpaceWire IP 코어를 지원할 수 있으며 공간 환경에 특화된 플랫폼으로 현재 규제 요구 사항을 충족할 수 있다.

데이터 인터페이스

●시스템 클럭 주파수만큼 Rx 비트 전송률이 높은 x4

●Tx 클럭 주파수는 100MHz-625MHz 사이

●단독 클럭 필드

FIFO 배치

●Tx FIFO 깊이 설정 가능: 64바이트에서 16384바이트

●RX FIFO 깊이 설정 가능: 64바이트에서 16384바이트

인터페이스

●AXI 스트림 (데이터)

●AXI-4 Lite (구성 및 관리)

성능

●최대 200Mbps의 링크 속도

SoC-e의 SMARTcia 보드는 SpaceWire IP 코어를 지원할 수 있으며 공간 환경에 특화된 플랫폼으로 현재 규제 요구 사항을 충족할 수 있다.

배포 지원

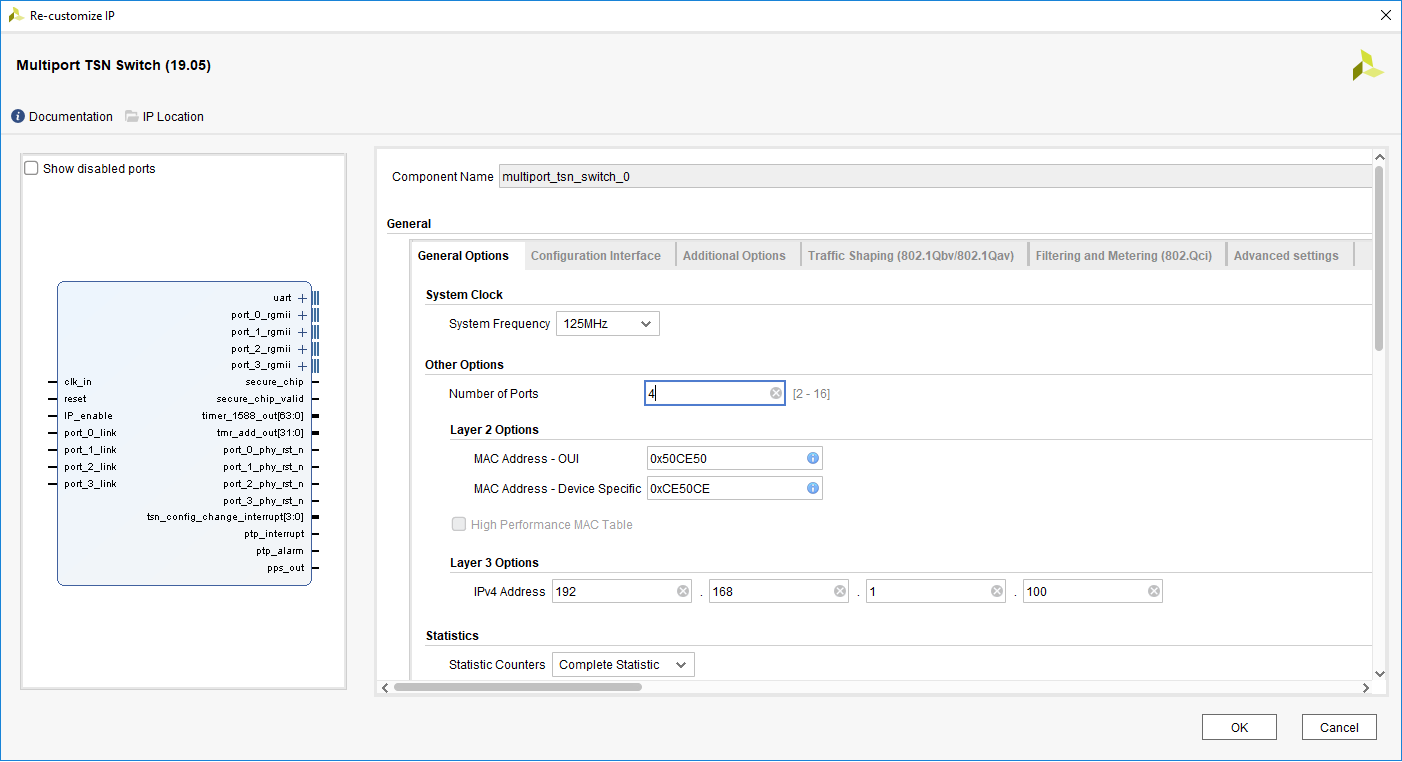

이하 Xilinx FPGA 시리즈는 SpaceWire IP 지지한다.

●7-Series(Zynq,Spartan,Artix,Kintex,Virtex)

●Ultrascale(Kintex,Virtex)

●Ultrascale+(Zynq MPSoC,Kintex,Virtex)

●XQR 시리즈(스페이스급 FPGA):Virtex-5QV and Virtex

●7-Series(Zynq,Spartan,Artix,Kintex,Virtex)

●Ultrascale(Kintex,Virtex)

●Ultrascale+(Zynq MPSoC,Kintex,Virtex)

●XQR 시리즈(스페이스급 FPGA):Virtex-5QV and Virtex

다운하기

SpaceWire IP 코어