IRIGtimeM: IRIG-B 마스터 IP 코어

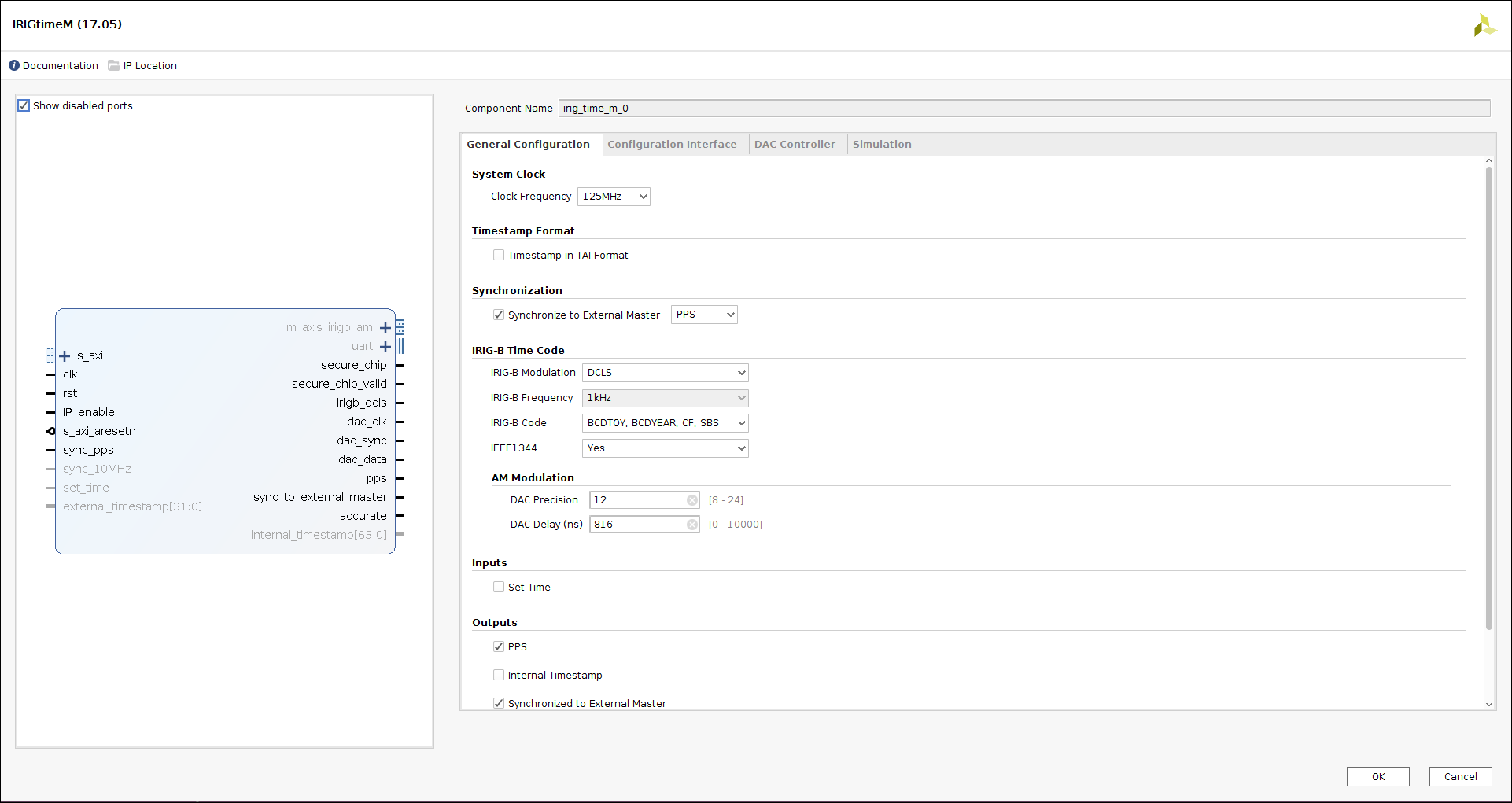

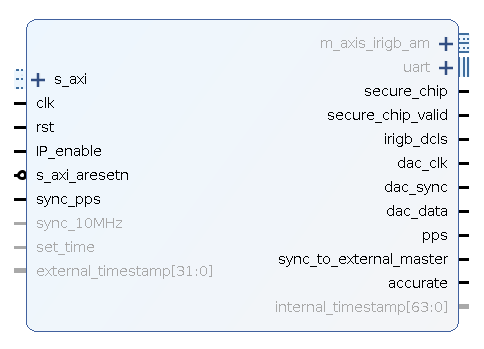

SOC-E SocTek 시리즈 IRIGtimeM은 FPGA 장치에서 IRIG 200-04 준수 시간 동기화 마스터를 가능하게 합니다. 이 IRIG-B 마스터 IP는 모든 IRIG-B 인코딩 표현식과 DCLS 및 AM 변조를 지원하도록 설계되어 최대한의 유연성을 제공합니다.

SOC-E SocTek 시리즈 IRIGtimeM은 구성에서 선택된 IRIG-B 타임코드에 따라 필수 및 선택 시간 정보(초, 분, 시, 일, 연, 제어 기능, 이진 직선 초)를 포함하여 초당 IRIG-B 프레임을 생성합니다. 이 IP는 자율 운영을 제공하도록 설계되었으며 가능한 한 적은 설정이 필요합니다.

소개

샘플 그래프

소개

주요 특징:

- IRIG 200-04 준수 시간 동기화 마스터

- DCLS 및 AM 변조가 지원됩니다

- 연도 정보, 제어 기능, 순수 이진 초를 포함한 모든 IRIG-B 인코딩 표현식이 지원됩니다

- 출력 유형(IRIG-B 타임코드)은 구현 전과 동적 시스템 모두에서 구성할 수 있습니다

- 나노초 정확도를 제공하는 정밀 IRIG-B 출력

- IP 초기 설정용 32비트 타임스탬프 입력

- 테스트용 주기적 펄스 출력

자세한 정보는 홍커를 통해 info@intelnect.com 문의해 주시기 바랍니다

샘플 그래프

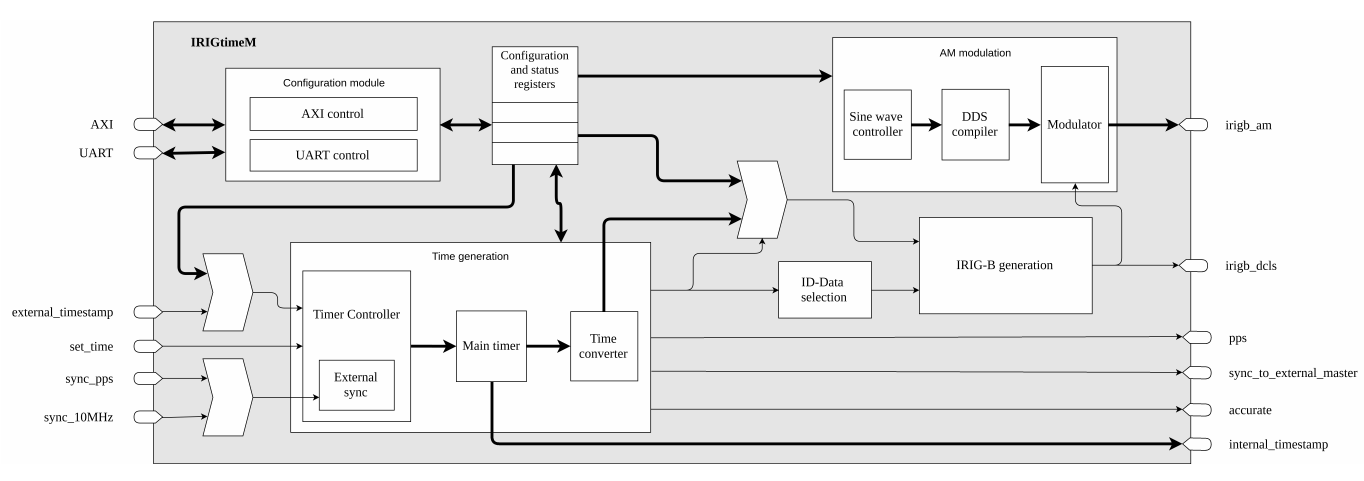

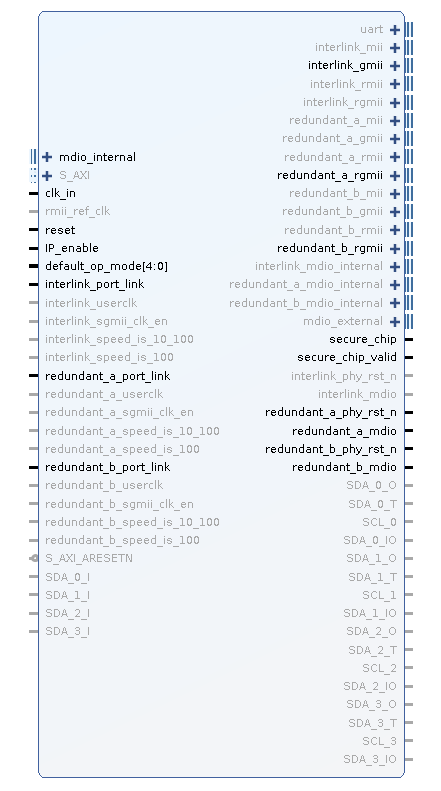

SOC-E SocTek 시리즈 IRIGtimeM IP 코어 블록 다이어그램

SOC-E SocTek 시리즈 제품 추천

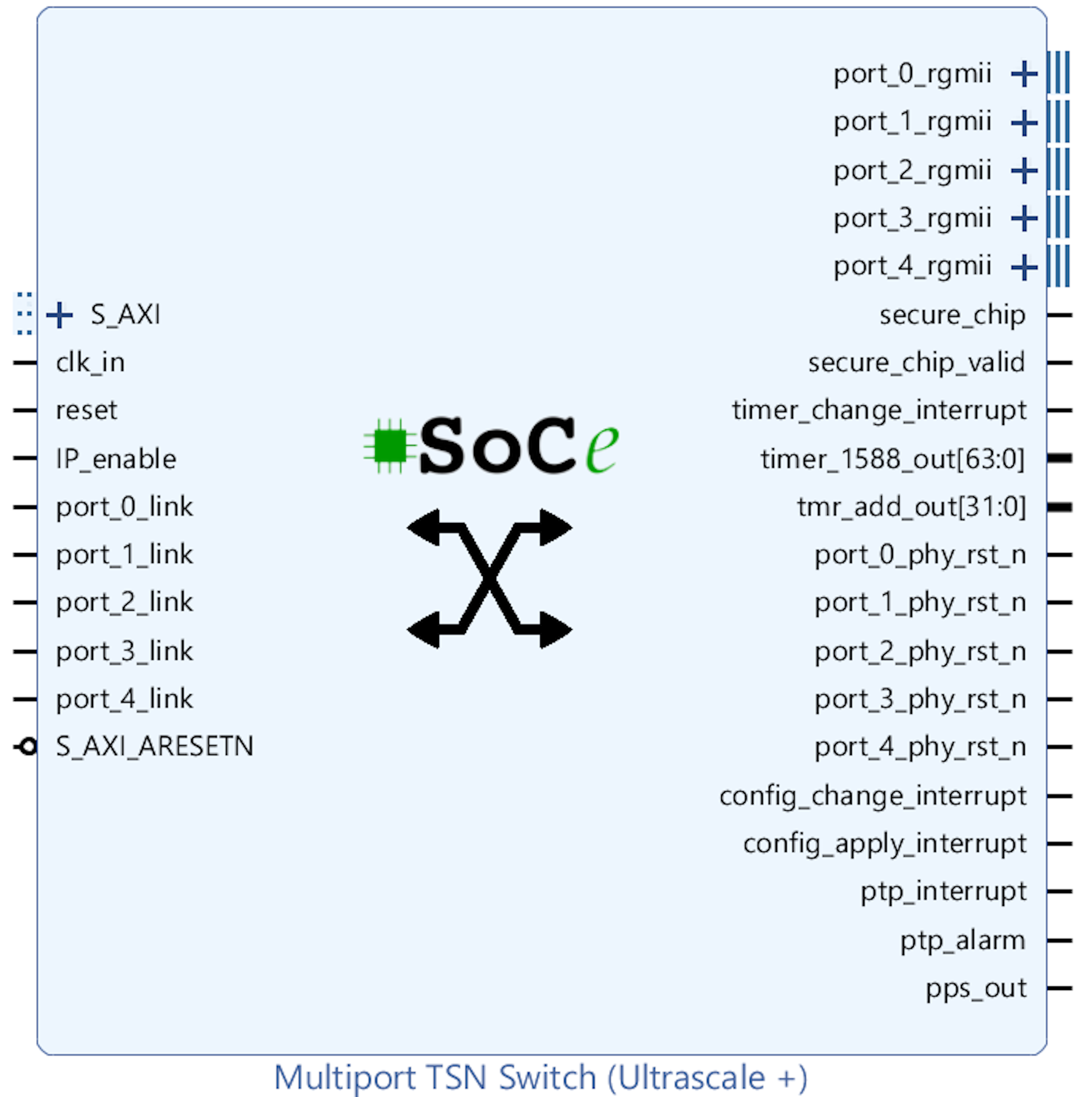

MTSN IP코어

다양한 TSN 프로토콜 명세를 구현하

는 포괄적인 TSN 솔루션입니다

HSR/PRP/PTP IPcore

신뢰할 수 있는 이더넷 통신을 위한 고가용성, 원활한 중복성, 병렬 중복 프로토콜 표준을 가능하게 합니다

네트워크 관리/네트워크 관

리 IP코어

프로그래머블 하드웨어 플랫폼용 이더넷 스위치 IP 코어

더 많은 IPcore 솔루션

설계 및 디버깅 시간을 줄이고 개발 과정을 가속화합니다