MultiSync IP Core:코어 시간 동기화 중복성

SOC-E SocTek 시리즈 멀티싱크 IP 코어는 모든 시나리오에서 최대 유연성을 위해 서브마이크로초 단위의 시간 동기화를 제공하는 다중 프로토콜 중복 시간 동기화 코어입니다. IEEE 1588-2008 (PTPv2) 및 IRIG-B 시간 동기화 프로토콜을 사용하여 시간 동기화를 제공할 수 있습니다.

SOC-E SocTek 시리즈 MULTI싱크는 SOC-E SocTek 시리즈 HSR-PRP 스위치, TSN 스위치, 비관리 이더넷 스위치 또는 관리형 이더넷 스위치 IP 코어와 함께 사용하여 이더넷 트래픽 스위칭 또는 HSR을 도입할 수 있습니다 그리고 PRP 중복성.

SOC-E SocTek 시리즈 멀티싱크 IP 코어의 다재다능함

SOC-E SocTek 계열의 MultiSync IP 코어의 다재다능함은 MULTI 동기화의 다양한 사용 사례를 상호 보완적으로 만듭니다:

- 시간 동기화 중복성을 제공하여 IP를 PTP 네트워크와 IRIG-B 마스터 모두에 연결할 수 있게 합니다. 사용자는 세 가지 사용 가능한 시간 소스(PTP, IRIG-B, FREE-RUN TIMER) 중에서 사용할 시간 소스를 선택할 수 있습니다.

- IP가 선택한 마스터와 동기화되는 동안 PTP와 IRIG-B 또는 IRIG-B와 PTP 간의 브리지 역할을 할 수 있습니다

- PTP 또는 IRIG-B 그랜드마스터 역할을 할 수 있습니다

다음 동기식 출력 옵션이 지원됩니다

- PTP: 이더넷입니다. 출력에 위치한 PTP 마스터 서버

- IRIG-B: IRIG-B 호환 신호. IRIG-B 출력의 종속 방송국

- 프리 런 타이머: 디지털 출력

다음 동기식 출력 옵션이 지원됩니다

- PTP: 스테이션 입력에서 이더넷 PTP

- IRIG-B: IRIG-B 호환 신호. IRIG-B 입력에 있는 슬레이브 스테이션

- 프리런 타이머: 디지털 입력

주요 특징:

- 다중 프로토콜 중복 시간 동기화

- IEEE 1588-2008 (PTPv2) 및 IRIG-B 시간 동기화 프로토콜 모두를 지원합니다

- 12가지 서로 다른 작동 모드

- 각 슬레이브와 연관된 3개의 독립적인 64비트 조절 타이머. (32비트 서브나노초 주파수 조정.)

- 초당 한 번의 펄스 출력을 제공합니다

- 이벤트 타임스탬프 지원 (최대 4개의 서로 다른 이벤트가 동시에 진행됨)

- 최대 4개의 서로 다른 알람을 동시에 감지 지원합니다

PTP 기능

- 10/100/1000 Mbps 이더넷 동작 지원

- 지원되는 AXI-S 인터페이스:

- 1 GB 이더넷: 8비트 데이터 폭

- 10 Gb 이더넷: 64비트 데이터 폭

- 이더넷 프레임에 서문이 포함되는지 선택하세요

- 16비트 FIFO 깊이. 초과 기록을 방지하기 위해 이전 타임스탬프 값을 저장하세요

- 종단 간 및 점대점 지연 메커니즘 지원

- PTP는 레이어 2(이더넷)와 레이어 3(IPv4) 인터페이스에서 지원됩니다

- VLAN 태그에 대한 PTP 메시지 지원

- IEEE1588 프로필: 기본값, 전력, 전력 유틸리티 (IEC61850-9-3), AS

IRIG-B 슬레이브 기능

- DCLS 및 AM 변조가 지원됩니다

- AM 신호의 내부 필터링

- 연도 정보, 제어 함수, 직접 이진 초를 포함한 모든 IRIG-B 인코딩 표현식이 지원됩니다

- IEEE-1344 확장 지원

- 입력 유형(IRIG-B 타임코드)은 사전 구현 및 동적 설정 모두 가능합니다

- SPI, QSPI, MICROWIRE 프로토콜과 호환되는 범용 ADC 컨트롤러를 구현하세요

IRIG-B 마스터 기능

- DCLS 및 AM 변조가 지원됩니다

- 연도 정보, 제어 함수, 직접 이진 초를 포함한 모든 IRIG-B 인코딩 표현식이 지원됩니다

- IEEE1344 확장 지원

- 출력 유형(IRIG-B 타임코드)은 구현 전과 동적 모두에서 구성할 수 있습니다

- SPI, QSPI, MICROWIRE 프로토콜과 호환되는 범용 DAC 컨트롤러를 구현하세요

무료 실행 타이머 기능

- 완전 사용자 관리 (시간 및 주파수 조정)

자세한 정보는 홍커를 통해 info@intelnect.com 문의해 주시기 바랍니다

지원되는 자일링스 FPGA 시리즈 및 평가 보드

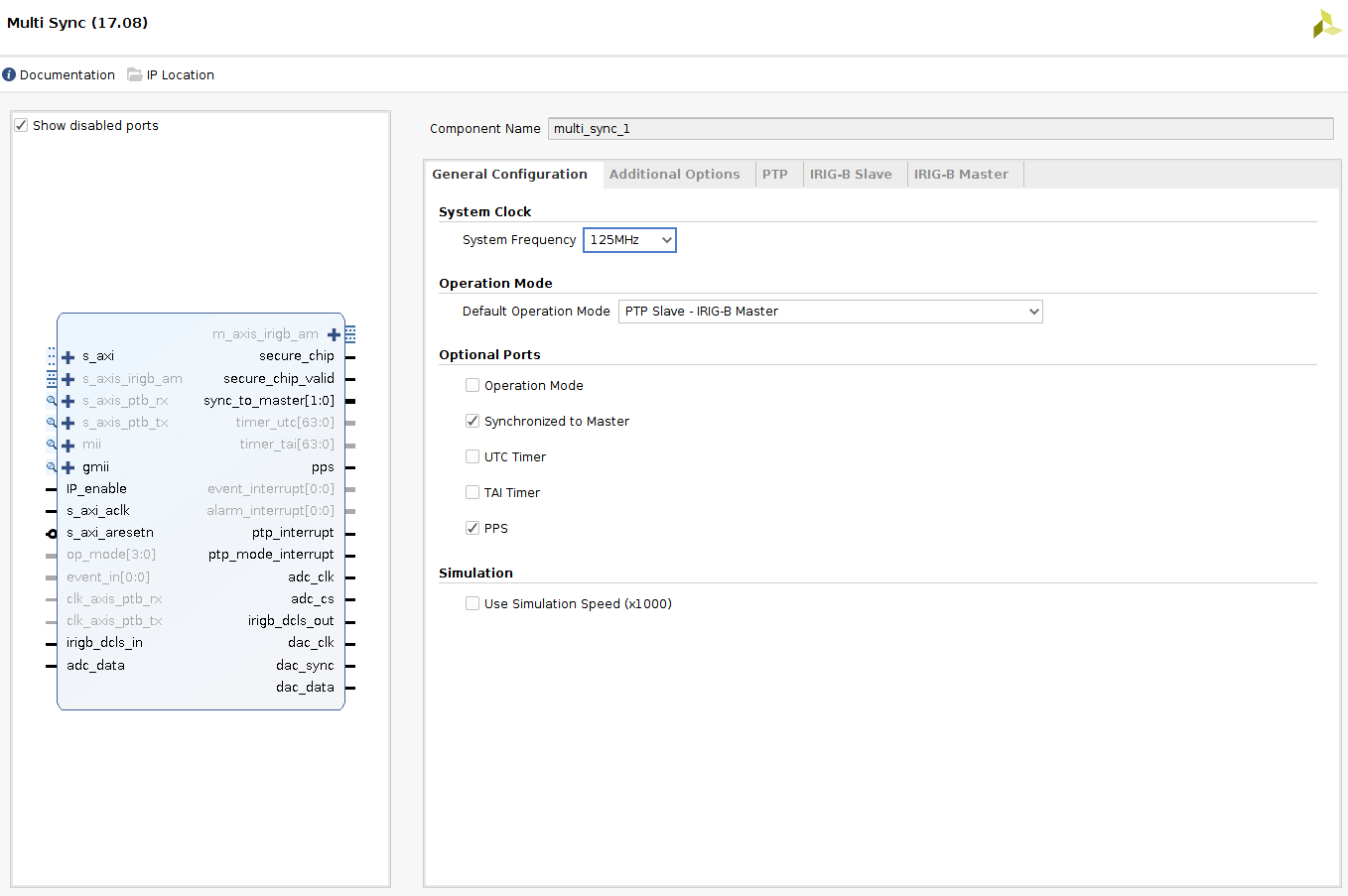

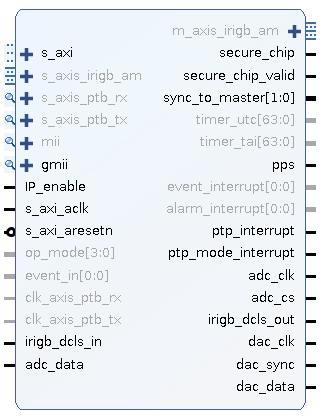

SOC-E SocTek 시리즈 MULTIsync는 새로운 Xilinx Vivado 도구를 활용하여 FPGA 설계에 쉽게 통합할 수 있도록 설계되었으며, 이 도구는 그래픽 사용자 인터페이스에서 IP 코어를 사용하고 IP 파라미터를 간단하게 구성할 수 있습니다.

다음 Xilinx FPGA 시리즈는 SOC-E SocTek 시리즈 MULTI Sync를 지원합니다:

- 7 시리즈 (Zynq, Spartan, Artix, Kintex, Virtex)

- 하이퍼스케일 (킨텍스, 버텍스)

- 울트라스케일+ (Zynq MPSoC, Kintex, Virtex)

- 버살 ACAP

참조 디자인으로 지원되는 보드:

- SoC-e SMARTzynq 모듈 (권장)

SOC-E SocTek 시리즈 제품 추천

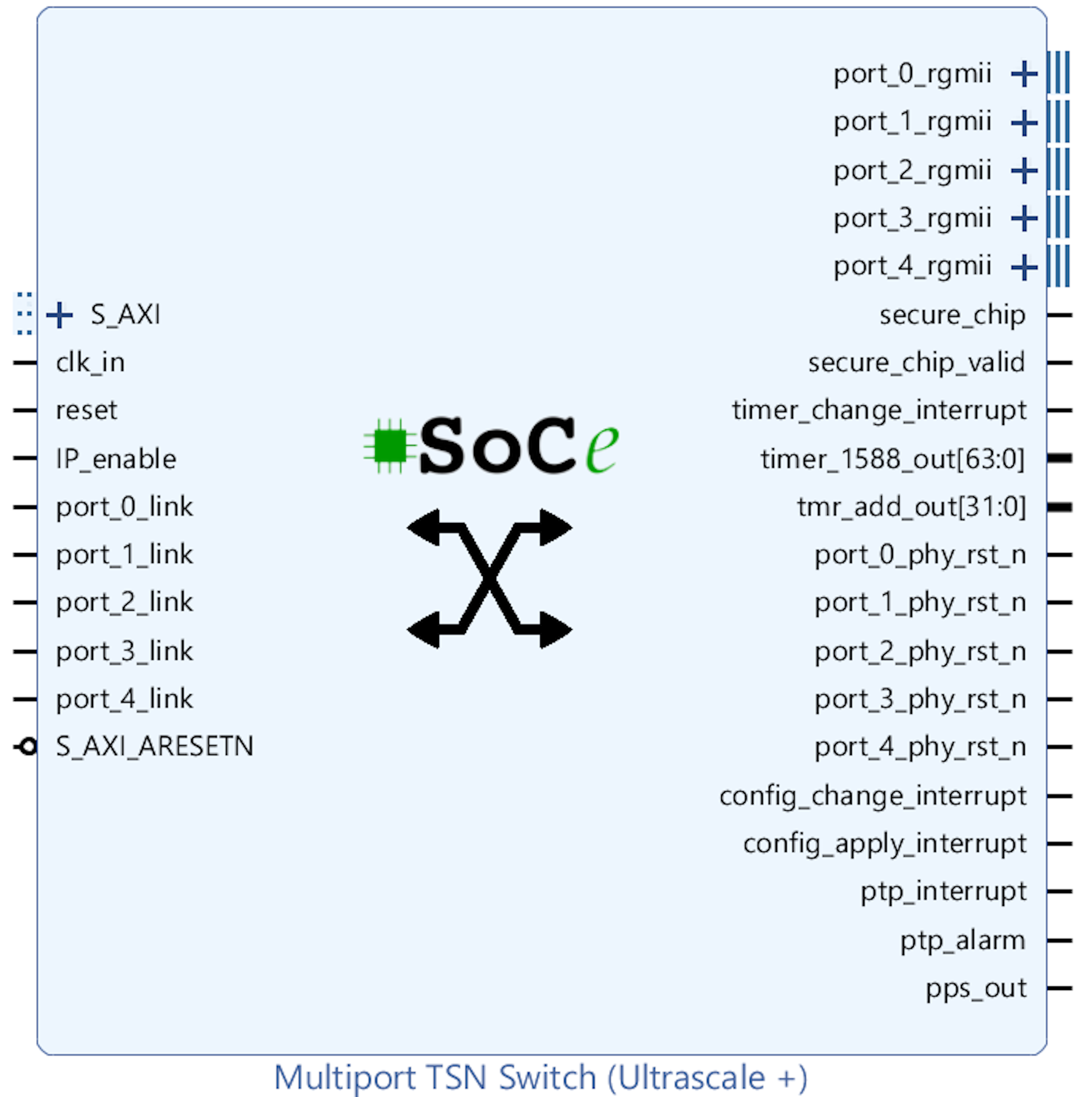

MTSN IP코어

다양한 TSN 프로토콜 명세를 구현하

는 포괄적인 TSN 솔루션입니다

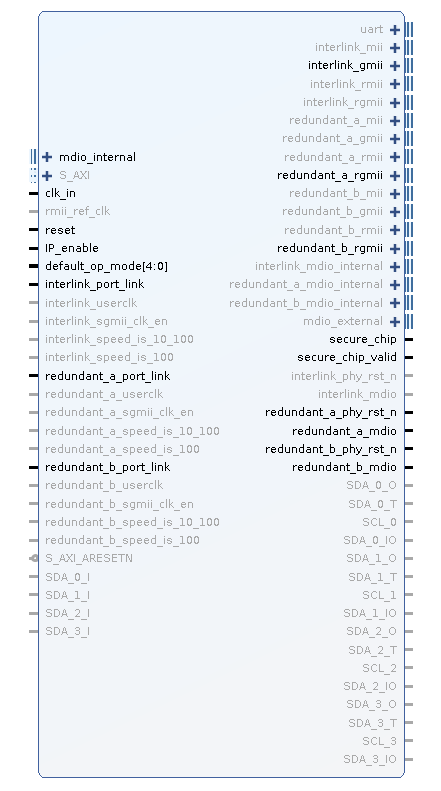

HSR/PRP/PTP IPcore

신뢰할 수 있는 이더넷 통신을 위한 고가용성, 원활한 중복성, 병렬 중복 프로토콜 표준을 가능하게 합니다

네트워크 관리/네트워크 관

리 IP코어

프로그래머블 하드웨어 플랫폼용 이더넷 스위치 IP 코어

더 많은 IPcore 솔루션

설계 및 디버깅 시간을 줄이고 개발 과정을 가속화합니다