정확한 시간 기반 IP 코어: IEEE1588v2 일반 및 경계 시계

SOC-E SocTek 시리즈 PreciseTime Basic은 IEEE1588-2008 v2 준수 Xilinx FPGA 클럭 동기화 IP 코어입니다. IEEE 1588 메시지의 타임스탬프를 정확히 표시하고 호환되는 타이머를 제공합니다. 이 모든 프로세스는 하드웨어 모듈에 의해 수행됩니다.

SOC-E SocTek 시리즈 프리스타임 베이직 IP는 다양한 하드웨어 및 소프트웨어 요소로 구성됩니다:

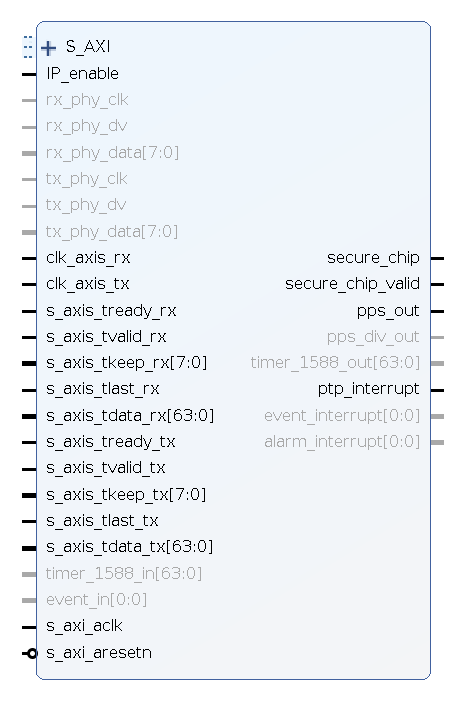

- 하드웨어 타임스탬프 유닛(TSU)은 IEEE 1588 이벤트 메시지를 정확하게 시간표 표시할 수 있으며, 서브마이크로초 정확도로 조절 가능한 타이머를 제공합니다. 사실, Soc-E SocTek 시리즈인 PreciseTimeBasic은 TSU의 PTB TSU와 PTBLite TSU 두 가지 버전으로 제공됩니다.

Soc-E SocTek 계열의 프리스타임 베이직 IP는 다양한 하드웨어 및 소프트웨어 요소로 구성되어 있습니다:

- 하드웨어 타임스탬프 유닛(TSU)은 IEEE 1588 이벤트 메시지를 정확하게 시간표 표시할 수 있으며, 서브마이크로초 정확도로 조절 가능한 타이머를 제공합니다. 사실, Soc-E SocTek 시리즈인 PreciseTimeBasic은 TSU의 PTB TSU와 PTBLite TSU 두 가지 버전으로 제공됩니다.

- 소프트웨어 PTP 참조 설계. SOC-E는 Linux PTP 하드웨어 클럭(PHC) 서브시스템을 사용하여 TSU에 접근할 수 있는 리눅스 커널 패치를 제공합니다. 추가 기능을 갖춘 오픈 소스 LinuxPTP 소프트웨어 스택의 수정된 버전도 제공됩니다. 모듈식 설계 덕분에 다른 운영국으로의 포팅이 가능합니다.

![PTB TSU 被设计为连接到 MAC 和 PHY 之间的介质独立接口 ([G]MII),解析所有以太网帧并检查哪些帧是 IEEE 1588。](https://z1.ax1x.com/2023/11/15/piYaiQA.png)

지원되는 자일링스 FPGA 시리즈 및 평가 보드

다음 Xilinx FPGA 계열은 SOC-E SocTek 시리즈 PreseTimeBasic을 지원합니다:

새로운 Xilinx Vivado 도구를 활용하여 FPGA 설계에 쉽게 통합할 수 있도록 설계되었으며, 그래픽 사용자 인터페이스에서 IP 코어를 사용하고 IP 파라미터를 간단하게 구성할 수 있습니다.

IEEE 1588 시스템에서 최종 정확도는 여러 요인(로컬 클럭의 주파수 및 품질, 데이터 체인 내 타임스탬프 위치 등)에 따라 달라집니다. 참고로, 다음 다이어그램은 상업용 그랜드마스터 장치가 생성하는 PPS와 ARM 프로세서에서 LinuxPTP 소프트웨어 스택을 실행하고 PreciseTimeBasic을 사용하는 Zedboard Avnet Devopment 플랫폼에서 생성하는 PPS 간의 측정 오차를 보여줍니다 하드웨어 지원 타임스탬프(+/- 50 ns)를 수행합니다.

하드웨어 기능:

- 10/100/1000Mbps/AXI-Stream 인터페이스 지원 (10Gbps/25Gbps용)

- 32비트 초 / 32비트 나노초 카운터

- 32비트 서브나노초 주파수 조정

- 초당 한 번의 펄스 출력을 제공합니다

- 선택 가능한 주파수 출력 (1 KHz/2 KHz/4 KHz/8 KHz/16 KHz/32 KHz)

- 최저 FPGA 자원 활용률

- 경고 생성

- 이벤트 타임스탬프

소프트웨어 기능:

- 일반적인 클럭(슬레이브 및 마스터) 동작

- 종단 간 및 점대점 지연 메커니즘 지원

- PTP는 레이어 2(이더넷)와 레이어 3(IPv4) 인터페이스에서 지원됩니다

- HSR-PRP 및 관리형 이더넷 IP 코어와 함께 사용할 수 있습니다

- VLAN 지원

- 산업 프로필: 기본값, 전력, 전력 유틸리티 IEC 61850-9-3, IEEE 802.1AS

- 차량 프로필: IEEE 802.1AS 범용 PTP(gPTP) 프로파일

- 엔터프라이즈 프로필/5G/통신 아카이브:G.8265.1, G.8275.1, and G.8275.2

IRIG-B 슬레이브 기능

- DCLS 및 AM 변조가 지원됩니다

- AM 신호의 내부 필터링

- 연도 정보, 제어 함수, 직접 이진 초를 포함한 모든 IRIG-B 인코딩 표현식이 지원됩니다

- IEEE-1344 확장 지원

- 입력 유형(IRIG-B 타임코드)은 사전 구현 및 동적 설정 모두 가능합니다

- SPI, QSPI, MICROWIRE 프로토콜과 호환되는 범용 ADC 컨트롤러를 구현하세요

IRIG-B 마스터 기능

- DCLS 및 AM 변조가 지원됩니다

- 연도 정보, 제어 함수, 직접 이진 초를 포함한 모든 IRIG-B 인코딩 표현식이 지원됩니다

- IEEE1344 확장 지원

- 출력 유형(IRIG-B 타임코드)은 구현 전과 동적 모두에서 구성할 수 있습니다

- SPI, QSPI, MICROWIRE 프로토콜과 호환되는 범용 DAC 컨트롤러를 구현하세요

무료 실행 타이머 기능

- 완전 사용자 관리 (시간 및 주파수 조정)

자세한 정보는 홍커를 통해 info@intelnect.com 문의해 주시기 바랍니다

제품 추천

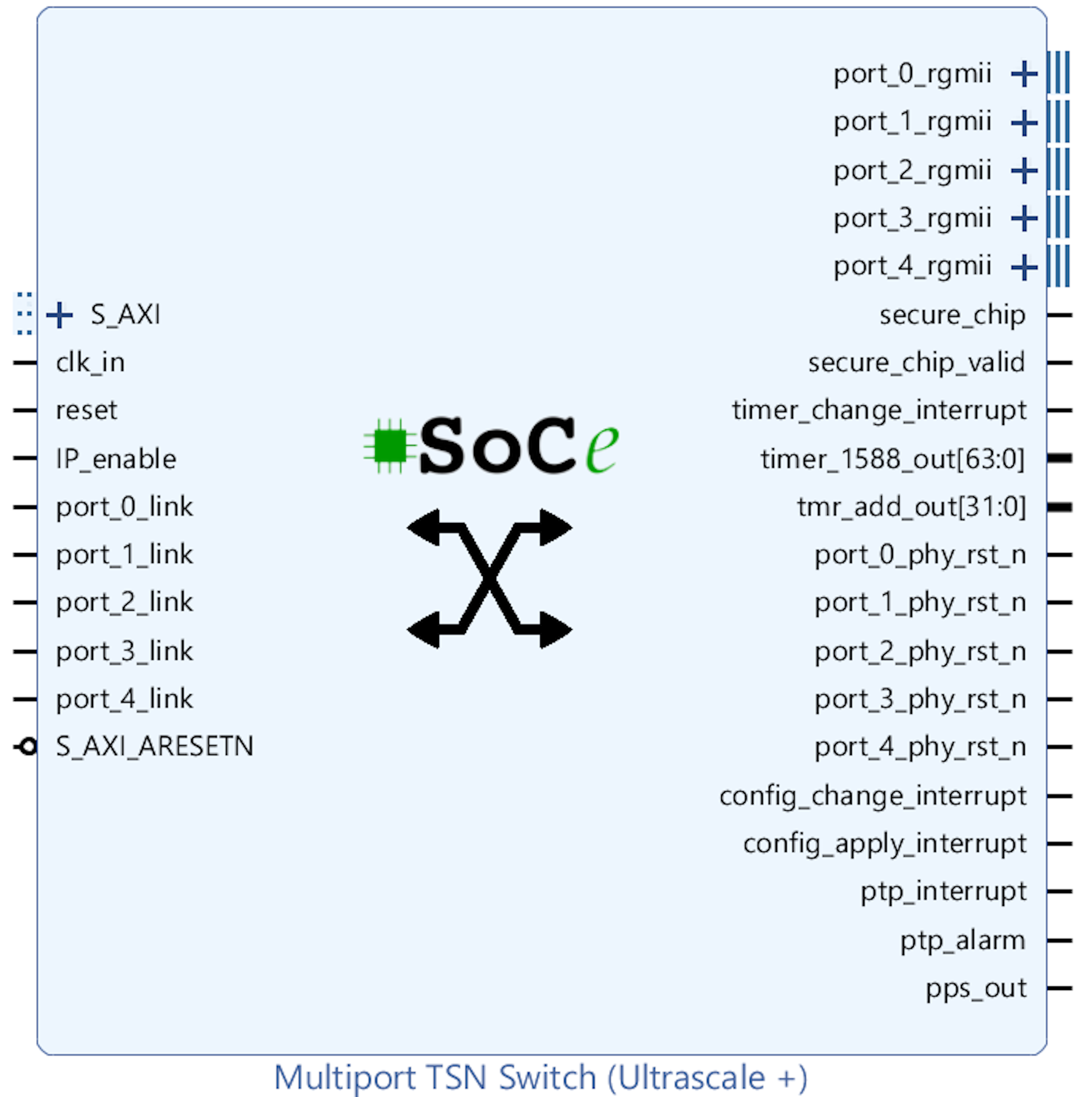

MTSN IP코어

다양한 TSN 프로토콜 명세를 구현하

는 포괄적인 TSN 솔루션입니다

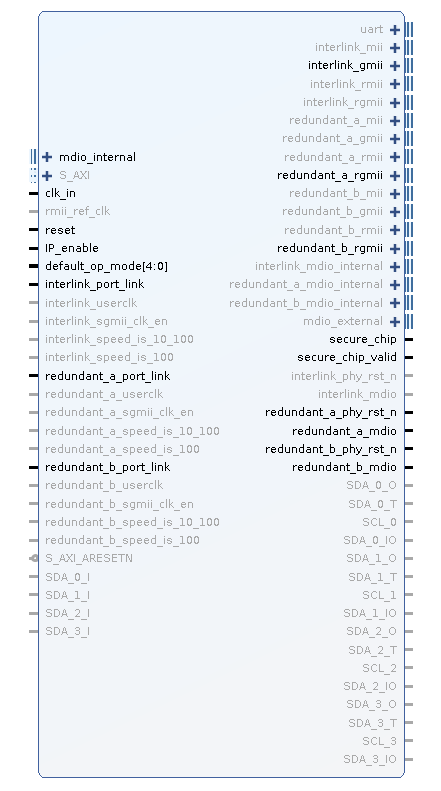

HSR/PRP/PTP IPcore

신뢰할 수 있는 이더넷 통신을 위한 고가용성, 원활한 중복성, 병렬 중복 프로토콜 표준을 가능하게 합니다

네트워크 관리/네트워크 관

리 IP코어

프로그래머블 하드웨어 플랫폼용 이더넷 스위치 IP 코어

더 많은 IPcore 솔루션

설계 및 디버깅 시간을 줄이고 개발 과정을 가속화합니다