SASCrypt – IEC 61850/62351 변전소 자동화 시스템을 위한 암호 IP 코어

- 레이어 2 IEC61850 GOOSE와 SMV(샘플 측정) 암호화, 복호화 및 인증

- 고성능 AES-GCM 엔진

- 마이크로초 거리 지연

- 유연한 맞춤화:

- 보안 처리되어야 하는 IEC 61850 메시지 유형

- 곱셈 지연 (타이밍 최적화)

- 곱셈 엔진 (자원 사용)

- 최대 100개의 서로 다른 데이터셋에 대한 키 저장 및 관리 로직

Xilinx Vivado 도구에서 사용할 수 있는 SOC-E SocTek 시리즈 SASCrypt IP

SOC-E SocTek 시리즈 SASCrypt IP는 새로운 Xilinx Vivado 도구를 활용하여 FPGA 설계에 원활하게 통합되도록 설계되었으며, 이 도구는 그래픽 사용자 인터페이스에서 IP 코어를 사용하고 IP 매개변수를 간단하게 구성할 수 있습니다.

다음 Xilinx FPGA 계열은 SASCrypt IP를 지원합니다:

- 6시리즈(스파르탄,버텍스)

- 7시리즈(Zynq, Spartan, Artix, Kintex, Virtex)

- 울트라스케일(킨텍스, 버텍스)

- Ultrascale +(Zynq MPSoC, Kintex, Virtex)

제품 설명:

SOC-E SocTek 시리즈 IEC 61850/62351 변전소 자동화 시스템 암호화(SAS Crypt) IP 코어는 변전소 자동화 시스템 및 신규 스마트 그리드 사이트에서 사용할 수 있는 실시간 트래픽을 보장합니다. 예를 들어, 이 시설 내 통합 장치나 IED 등 중요한 장비와 통신하는 데 사용되는 GOOSE 및 샘플 측정(SMV) 프레임워크를 보호할 수 있습니다. 이 IP는 상호 운용성을 보장하고 IEC 61850 보호된 트래픽과 보호되지 않은 트래픽이 동일한 네트워크 내에 존재할 수 있도록 하는 새로운 IEC 62351-6 표준을 구현합니다. 이 표준은 Layer 2 IEC 61850 프레임에 적용될 암호화 및 인증 메커니즘을 정의합니다. 이 저지연 IP 코어는 GOOSE 또는 SMV를 라인 속도로 암호화, 복호화, 인증할 수 있습니다.

IEC 62351 범위 내에서 매우 중요한 주제는 보호를 위한 키의 관리 및 배포입니다. SOC-E SocTek 계열의 SASCrypt IP 코어는 장치에 보안 키를 도입하는 다양한 시나리오를 가능하게 합니다. IP를 통한 키를 정적으로 수집하는 방식부터 IEC 62351-9: 전력 시스템 장비를 위한 사이버보안 키 관리에 정의된 완전 자동화된 보안 키 관리 솔루션에 이르기까지.

SASCrypt IP 코어인 SOC-E SocTek 계열은 이 작업에 최적화된 독자적인 저지연 암호 암호를 통합하고 있습니다. 이 암호 모듈은 최적의 자원 활용과 함께 필요한 성능을 제공하며 몇 마이크로초의 지연을 도입합니다. 실제로 SASCrypt IP는 지원되는 데이터 처리량과 합성 시 구현해야 하는 FPGA 자원 간의 트레이드오프를 허용합니다.

최적화 구현을 가능하게 하는 가장 관련 설정 가능한 매개변수는 다음과 같습니다:

- IEC 61850에 의해 반드시 보호되어야 하는 메시지 유형

- 비밀번호에 적용된 곱셈 지연

- 비밀번호에 사용된 곱셈 엔진

- 최대 100개의 서로 다른 IEC 61850 데이터셋에 대한 키 저장 및 관리 로직 구현 시나리오

보호 기능 외에도, SOC-E SocTek 시리즈 SASCrypt IP 코어는 IEEE 1588 V2 1단계 투명 클럭 포인트 투 포인트(P2P) 기능을 지원합니다. 이 기능은 PTP 프레임의 체류 시간과 각 링크의 지연 시간을 보상할 수 있게 해줍니다.

SOC-E SocTek 시리즈 SASCrypt IP 코어는 SOC-E SocTek 시리즈 MES IP 코어 및 SOC-E SocTek 시리즈 HSR-PRP 스위치 IP와 함께 사용하여 이더넷 스위칭 기능을 도입하고 장치에 보안을 통합할 수 있습니다.

- 풀 듀플렉스 10/100/1000 Mbps 이더넷 인터페이스

- 하프 듀플렉스 10/100 Mbps 이더넷 인터페이스

- MII/RMII/GMII/RGMII/SGMII/QSGMII 물리层设备 (PHY) 接口

- 1000 Mbps AXI-Stream 接口

- 铜缆和光纤介质接口:10/100/1000Base-T, 100Base-FX, 1000Base-X

- IEEE 1588v2 상태 없는 투명 시계 기능 (P2P – 레이어 2 / E2E – 레이어 2)

- 기본적으로 전력 유틸리티 프로필은 IEC 61850-9-3입니다

- 호환 SoC-e IEEE 1588 IP 内核(1588Tiny,PT B – PreseTimeBasic)

- MDIO, UART, AXI4-Lite 관리接口

- 드라이버는 IP 코어(*) 구매 시 제공됩니다

- SoC-e SMARTzynq 보드(추천)

SoC-e SMARTmpsoc 보드(추천)

SOC-E SocTek 시리즈 제품 추천

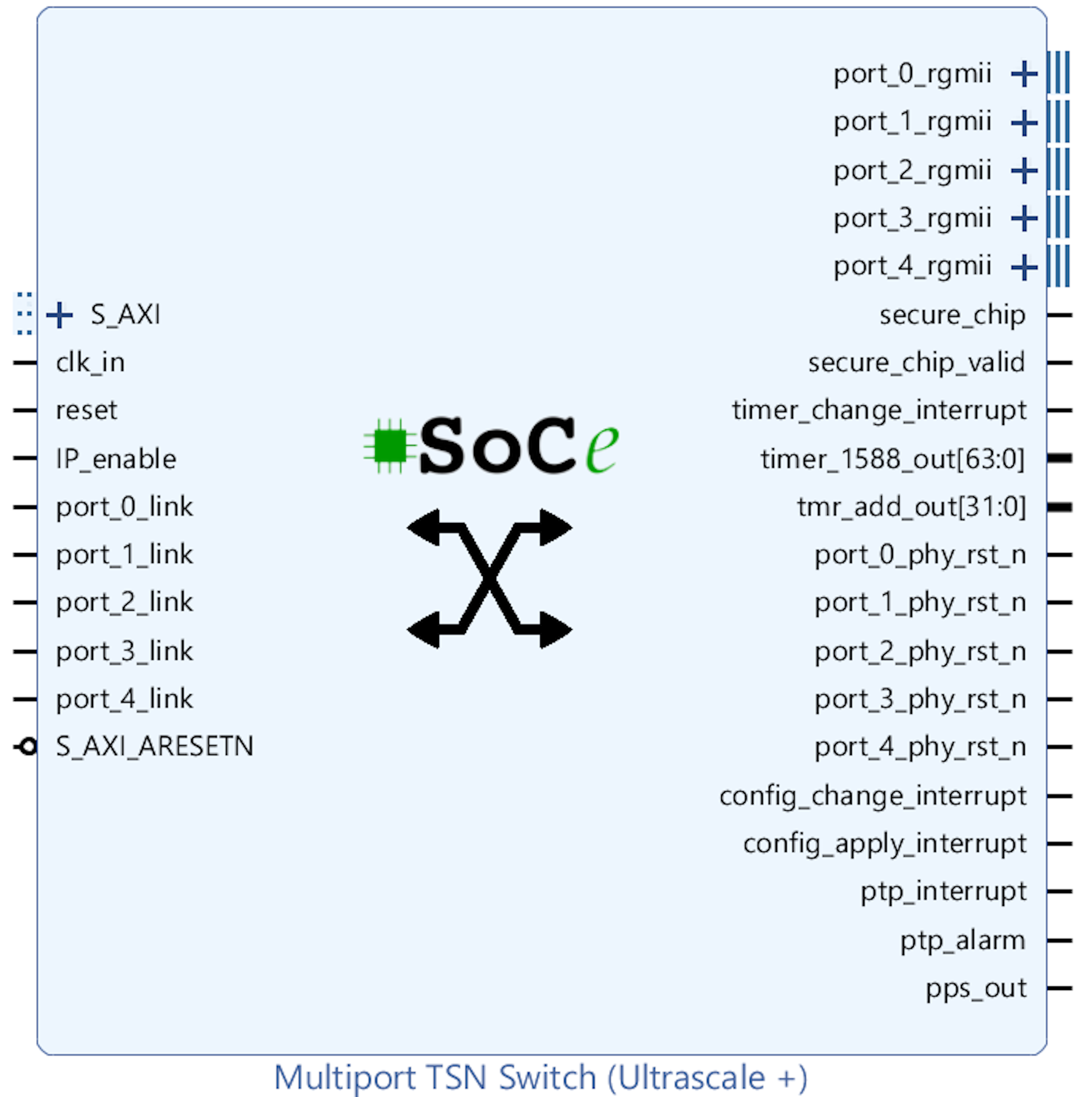

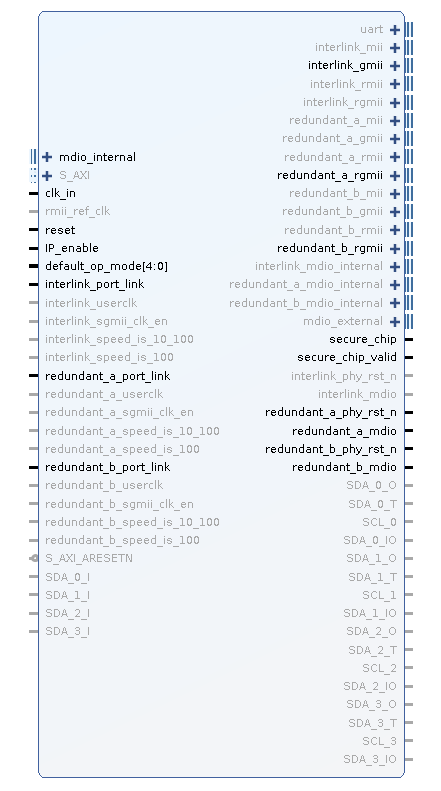

MTSN IP코어

다양한 TSN 프로토콜 명세를 구현하

는 포괄적인 TSN 솔루션입니다

HSR/PRP/PTP IPcore

신뢰할 수 있는 이더넷 통신을 위한 고가용성, 원활한 중복성, 병렬 중복 프로토콜 표준을 가능하게 합니다

네트워크 관리/네트워크 관

리 IP코어

프로그래머블 하드웨어 플랫폼용 이더넷 스위치 IP 코어

더 많은 IPcore 솔루션

설계 및 디버깅 시간을 줄이고 개발 과정을 가속화합니다