IPcore 개발 솔루션

IP 코어(지식재산권 코어)는 특정 회로 기능을 구현하는 하드웨어 설명 언어 프로그램입니다. 이 프로그램은 집적 회로 제조 공정에 독립적이며, 다양한 반도체 공정에 이식하여 집적 회로 칩을 생산할 수 있습니다. 따라서 IP 코어의 활용은 점점 증가하는 추세이며, IP 코어의 재사용은 제품 출시 기간을 크게 단축시켜 줍니다.

단순화하다

설계 및 디버깅 시간 단축 개발 프로세스 가속화

매우 유연함

VHDL 코드는 풍부한 일반 매개변수를 제공합니다

호환성이 좋습니다

다양한 프로토콜 사양을 지원하며, 저가형 FPGA에 구현할 수 있습니다

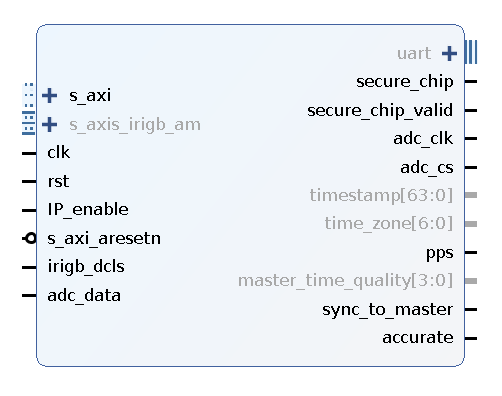

심상

Vivado IPI는 GUI 인터페이스를 제공하므로 그래픽 설정을 지원합니다

SOC-E SocTek 시리즈

MTSN IPcore

다양한 TSN 프로토콜 사양을 구현할 수 있는 포괄적인 TSN 개발 솔루션입니다

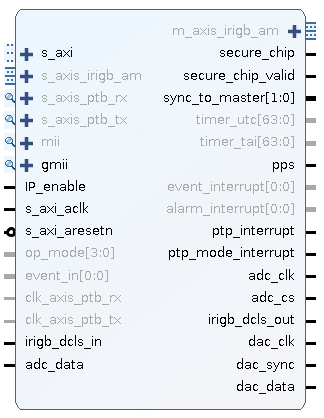

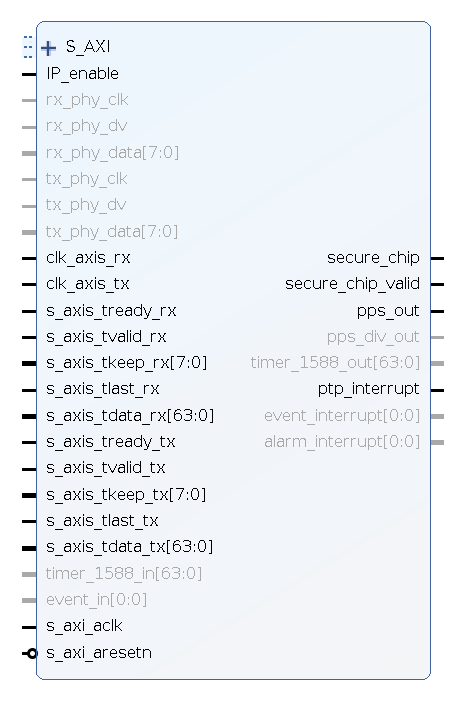

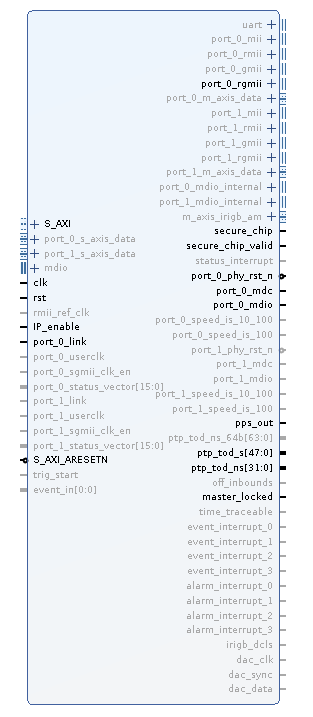

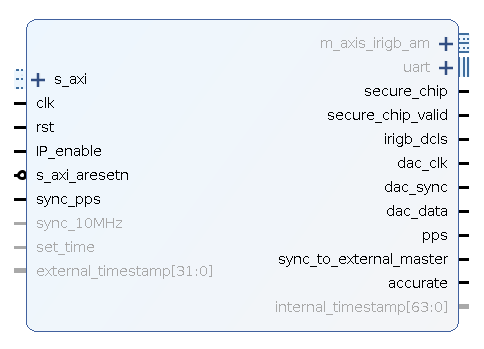

SocTek의 SOC-E 시리즈 MTSN IP 코어는 TSN 엔드포인트 또는 TSN 브리징 구현을 생성할 수 있는 유연한 HDL 코드입니다. 이 IP는 최적의 기능-리소스 균형을 위한 풍부한 공통 파라미터 세트를 제공합니다. Vivado IPI는 GUI 인터페이스를 제공하므로 이러한 공통 기능을 VHDL 수준 또는 그래픽 인터페이스를 통해 구성할 수 있습니다.

- 다양한 PHY 인터페이스를 사용할 수 있습니다: MII/RMII/GMII/RGMII/SGMII/QSGMII

- 스위칭 기능: 전이중 10/100/1000Mbps 이더넷 인터페이스; 최대 32개 포트, 각 포트는 서로 다른 데이터 전송 속도를 지원합니다

- IP 코어 구성 포트: 4가지 유형의 구성 관리 포트

SOC-E SocTek 시리즈

네트워크 IPcore

이더넷 통합 추세에 따라 산업, 에너지, 자동차, 항공우주, 통신 등 다양한 산업 분야에서 OT/IT 네트워크에 대규모 운영 이더넷 솔루션을 도입하고 있습니다. IPcore 개발 솔루션은 고객 제품의 출시 기간을 단축하고 설계 위험을 줄일 수 있습니다.

관리형/비관리형 IPcore

- 1G - 네트워크 관리 이더넷 스위치

- 10G - 네트워크 관리 이더넷 스위치

- 1G - 비네트워크관리 이더넷 스위치

고가용성 중복 네트워크

HSR/PRP/PTP IPcore

- 1G 네트워크 관리용 이중화 스위치

- 1G HSR/PRP 스위치

- 확정성 HSR 스위치

기타 네트워크화 IPcore

- AVB 자동차 이더넷 스위치

- SpaceWire 인코더/디코더

기타 IPcore

아래 링크를 클릭하여 자세히 알아보세요

SOC-E SocTek 시리즈 동기식 IPcore

복잡한 FPGA 설계를 테스트하고 검증하는 방법은 무엇일까요?

IP 코어 개발에는 IP 코어 명세 정의, 인터페이스 기반 설계, IP 코어 테스트 접근 구조 표준, IP 코어 검증 및 패키징 등 여러 핵심 기술이 포함됩니다. IP 코어 검증은 주로 참조 모델 및 테스트 플랫폼 구축을 시작으로 회귀 테스트 및 형식 검증을 수행하는 방식으로 진행됩니다. 참조 모델은 주로 시스템 기능 검증 및 RTL 모델과의 비교에 사용되며, 주로 Verilog HDL과 같은 언어를 사용하여 구축됩니다. 테스트 플랫폼 구축은 서브모듈 설계와 병행하여 진행되며, 검증 환경 설정 및 테스트 케이스 개발을 포함합니다. 테스트 환경과 테스트 케이스는 IP 코어의 동작 모델을 대상으로 디버깅되며, 이를 통해 RTL 수준의 IP 코어를 시뮬레이션하고 테스트할 수 있는 검증 환경과 테스트 케이스를 동시에 준비합니다.

시뮬레이션과 검증은 고품질 FPGA 기반 RTL 코딩 프로세스를 개발하는 데 필수적입니다. 아래 글에서는 설계 프로세스의 주요 단계를 공유하고 홍케(Hongke)의 이더넷 IP 코어 포트폴리오를 소개합니다.